VT技术

虚拟化技术(Intel VT-x)相关

0x01 硬件虚拟化的基本概念

VT是指Intel的硬件辅助虚拟化技术(Virtualization Technology),起初时为了提高VMware之类的软件虚拟化性能,由于VT技术引入了一个新的CPU层级Ring-1,所以其在安全方面也增加了很多应用。

1.1 概述

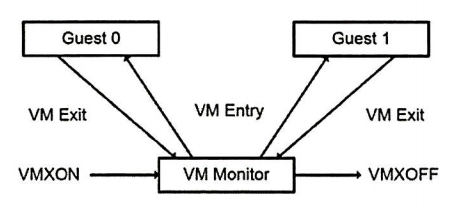

硬件虚拟化引入的新的CPU模式和虚拟化指令集能帮助VMM(Virtual Machine Monitor,虚拟机监视器)提升性能。Intel VT-x为CPU提供了(Virtual Machine Extension,虚拟机拓展)功能。在VMX中,新的CPU模式被称为Root模式(VMX Root Operation),该模式仅供VMM使用。Guest OS(子操作系统)运行在non-Root模式(VMX non-Root Operation)下。VMM可以截获Guest OS使用的特权指令和对硬件的访问,实现对系统资源的有效控制。

VMM通过虚拟机控制结构(Virtual-Machine Control Structure,VMCS)设置需要截获的硬件访问,例如指令,中断,内存访问和异常等。如果Guest OS在执行时触发了这些条件设置,将引起VM退出(#VMExit),此时CPU会从non-Root模式转换为Root模式,VMM会获取系统控制权并执行相应的处理程序。

当VMM执行结束后,将控制权返回给Guest OS,这成为VM进入(#VMEntry),CPU在虚拟化指令VMXON,VMXOFF的控制下开启或关闭VMX功能。

在硬件虚拟化中,有时称VMM为“Hypervisor”,专指在使用VT技术时创建的特权层,也就是Ring0之下的Ring-1.处在这个层次的代码能监视计算机的各种行为,如特权指令,内存访问,I/O访问等。因为操作系统是处于Ring0层,而Ring-1层可以监视操作系统的各种操作,所以Hypervisor的权限是大于操作系统的。

典型的Hypervisor例子类似于用WindowsSDK编写窗口程序。用WindowsSDK编写窗口程序分为下面5步。

- 调用RegisterClassEx注册窗口,这里,需要填写WndProc函数地址,用于在WndProc中处理各种各样的窗口消息。

- 调用CreateWindowsEx建立窗口。

- 调用ShowWindow,UpdateWindow显示窗口。

- 进入无线电消息循环,直到获取WM_QUIT时退出程序。

- 在WndProc中处理各种消息。

创建一个典型的VT技术Hypervisor例子其实和编写Windows窗口程序类似,大概分成下面4步。

- 分配VMXON区域和VMCS控制块。

- 填写VMCS控制块。VMCS控制块用于控制要监控什么特权指令,是否开启EPT机制,是否监控IO访问等。VMExitProc类似于窗口过程,在VMExitProc中处理各种各样的操作系统陷入事件,针对感兴趣的事件进行处理。

- 调用VMXLaunch启动虚拟机

- 当#VMExit事件时调用VMExitProc函数,处理各种感兴趣的虚拟机陷入消息。

1.2 相关结构和汇编指令

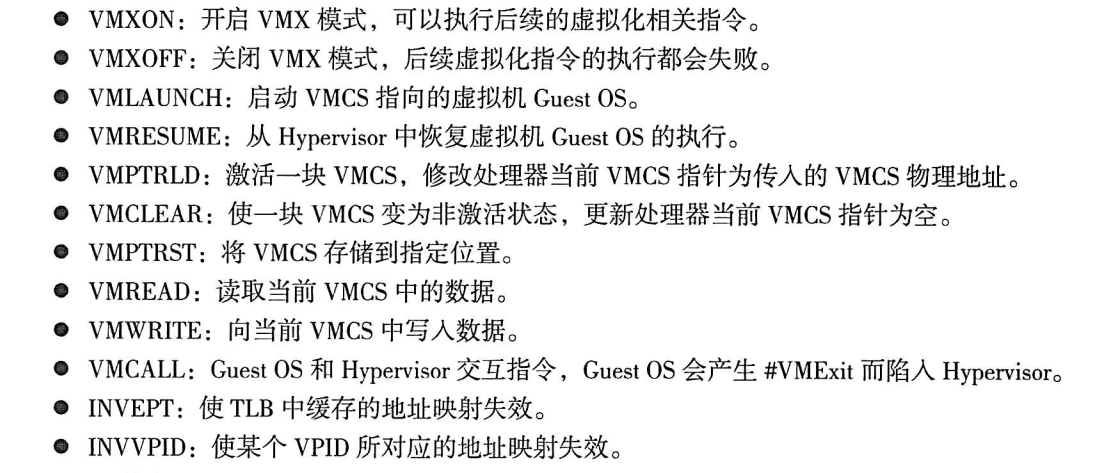

为了实现VT技术,Intel引入了一系列新的指令集。

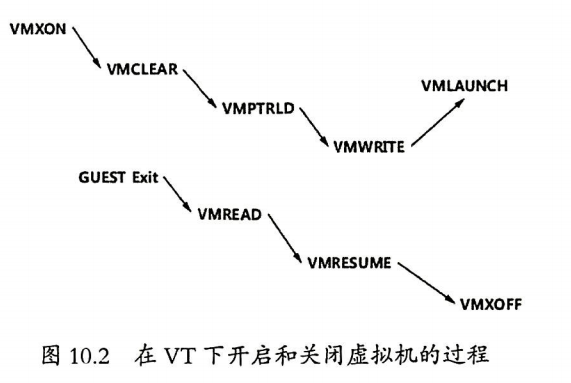

要进入IntelVT,必须打开VMX操作模式,打开VMX操作模式使用的就是VMXOn指令。只有能够使用VMXOn指令进入VMX模式,才表示CPU支持VT模式。当不在使用VT功能时,可以使用VMXOff关闭VMX模式。

当使用VMXOn指令进入VMX操作模式的时候,CPU处于Root模式,这时需要对GuestOS进行一些配置。然后,使用VMLaunch指令从Root模式转到non-Root模式。

在GuestOS中允许一段时间,如果产生了Hypervisor感兴趣的事件,就会产生#VMExit陷入Hypervisor。Hypervisor会对时间进行处理,处理完成调用VMResume重新#VMEntry到GuestOS中。这样周而复始的工作,直到调用VMXOFF指令关闭VMX模式为止。

由于CPU支持多GuestOS,所以需要有一个东西代表唯一的GuestOS,在VT中可以简单理解为每个VMCS代表一个GuestOS,为了操作VMCS,Intel又引入了几条指令。

当使用VMPTRLD指令将内存中的一块地址当成VMCS以后,这块内存不只是一块内存,而是代表了一个GuestOS。同时后续的一些VMCS操作指令也默认使用当前的VMCS地址,因为只有VMPTRLD参数时VMCS指针,后续的操作都是针对该块VMCS的,直到VMCLEAR指令将一块VMCS变为不活跃状态为止。

使用VMPTRLD指令装在一个VMCS后,还可以使用VMPTRST指令将当前的VMCS存储到指定的为止。当使用VMPTRLD指令装在一个VMCS后,就不能使用内存操作函数去操作VMCS所对应的内存了,而应该使用CPU提供的指令VMREAD和VMWRITE进行读写。

为了支持Hypervisor和GuestOS的交互,引入了VMCALL指令。这条指令会在GuestOS中产生一个#VMExit事件,从而陷入Hypervisor。

另外为了管理与VT相关的TLB指令,又引入了两条指令,分别是INVEPT和INVVPID。这两条指令配合使用可以管理TLB。

VT技术的虚拟化指令如下:

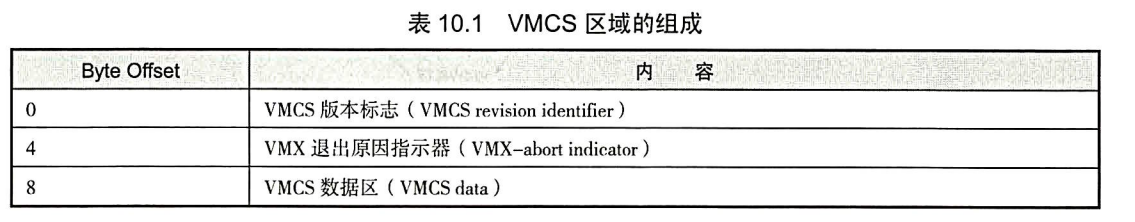

在VT技术中,VM控制块也称VMCS,可以简单理解:一个VMCS代表了一个虚拟机,可以控制VMCS来控制虚拟机的各种行为和属性。

由于CPU需要的信息比较多,导致VMCS的结构非常复杂。

VMCS区域的前4字节时版本标志,不同的VMCS格式对应的版本号不同,在使用VMCS区域前,应当设置VMCS版本标志,通常软件可以通过读取IA32_VMX_VASIC MSR寄存器来设置VMCS的标志。

在产生#VMExit事件时,如果遇到问题,系统就会发生VMX Abort事件。VMX推出原因指示器会指出发生VMX Abort事件的原因,这回导致该逻辑处理器进入关闭状态。对于一个已经激活的VMCS,一个VMX Abort事件不会导致VMCS数据区被修改,因此需要一种机制去判断是什么原因导致了VMX Abort事件。通常导致VMX Abort事件的原因包括保存客户虚拟机MSR寄存器失败,当前VMCS区域损坏,加载Hypervisor的MSR寄存器失败等。

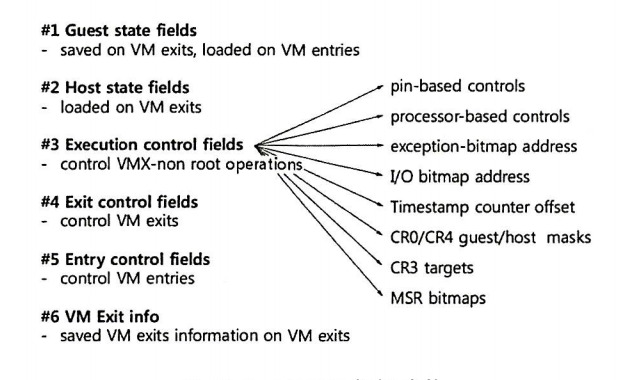

我们真正需要关心的时VMCS数据区,这个区域保存和控制了虚拟机的各种状态和行为,在这里控制感兴趣的特权指令,内存访问,IO访问等。Intel开发者手册将其分为6个部分。

1.2.1 虚拟机状态域(Guest-State Area)

当虚拟机GuestOS运行时,从这个区域加载虚拟机的各种状态值。当VM进入时,处理器状态从该域中加载,当虚拟机退出的时候,发生#VMExit事件,处理器状态保存在该区域中。

该区域需要保存的信息很多,除了通用寄存器值,还有一些有关CPU状态信息的寄存器信息,需要保存和恢复的寄存器信息(Guest Register State,客户机寄存器状态内容),以及CPU状态信息(Guest Non-Register State)。

1.2.2 宿主机状态域(Host-State Area)

产生#VMExit时,处理器状态从该域中加载。这个区域记录了所有Hypervisor的状态信息。这个区域保存的内容会在每次发生#VMExit事件的时候恢复到相应的寄存器中,以恢复Hypervisor的执行环境。与虚拟机状态域不同,宿主机状态域只能存储有关寄存器的信息。

1.2.3 虚拟机执行控制域(VM-Execution Control Fields)

在这里,可以设置各种推出条件,控制处理器在VMX non-Root模式中的行为,以及哪些事件会导致#VMExit陷入Hypervisor。可以设置感兴趣的异常,IO访问,MSR寄存器访问,CR3等事件,共26个字段。

如果需要拦截异常或MSR寄存器访问(例如IA32_SYSTENER_EIP者CR3寄存器访问),都要在此处进行配置。

1.2.4 虚拟机VMEntry控制域(VMEntry Control Fields)

该区域控制虚拟机#VMEntry事件发生时的行为,也就是从Hypervisor进入GuestOS时的行为,例如初始化是否进入x64模式。如果想认为的触发一个GuestOS异常中断,也可以在此处进行配置。

1.2.5 虚拟机VMExit控制欲(VM-Exit Control Fields)

该区域定义了在#VMExit事件发生后硬件立即要做的事情,主要包括两部分,分别是#VMExit基本操作控制设置和#VMExit MSR寄存器操作控制设置。

1.2.6 虚拟机VMExit信息域(VMExit Information Fields)

该区域是制度区域,用VMWRITE写入会失败。该区域包含最近#VMExit事件的相关信息,接受虚拟机退出信息,描述虚拟机推出原因。GuestOS产生#VMExit的线性地址和物理地址等。

1.3 EPT机制

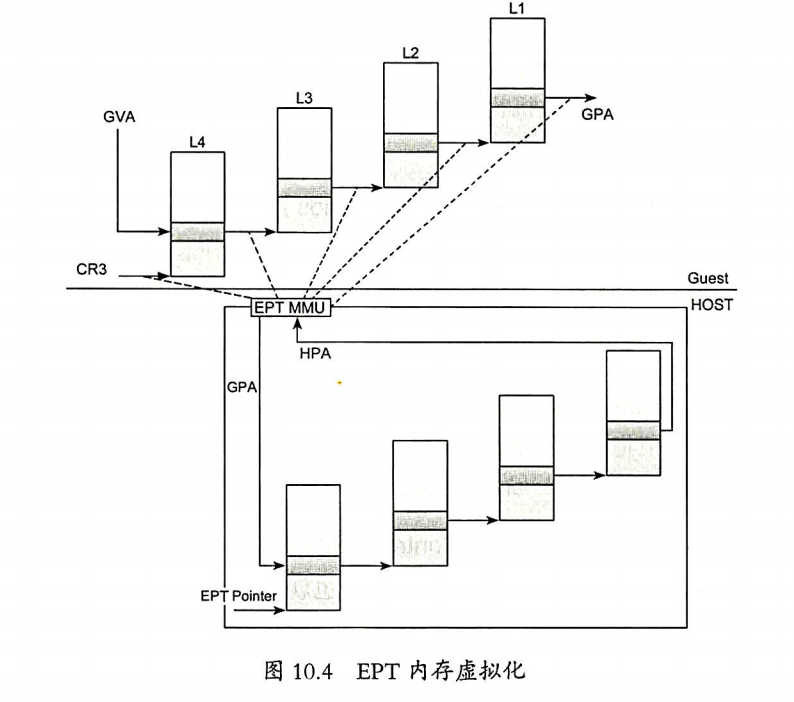

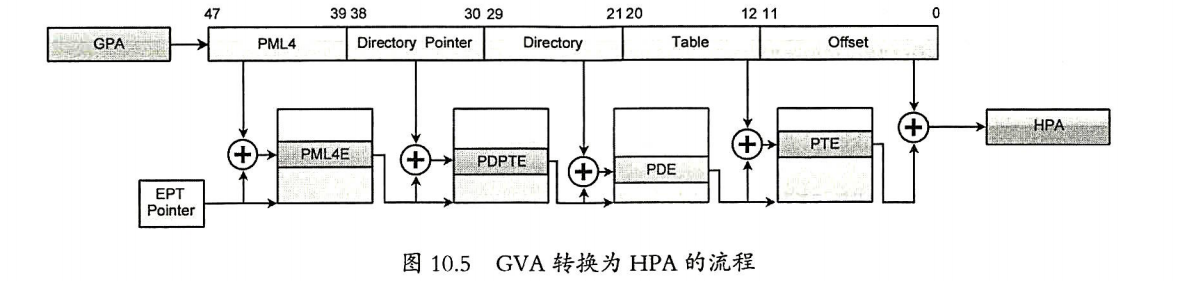

为了支持物理隔离GuestOS和提高虚拟机的执行效率,Intel在VT技术中引入了扩展页表技术(Extended Page Tables,EPT)。在虚拟化平台上,每个Guest OS都有独立的物理地址空间,每个Guest OS并不知道其他GuestOS的存在,就像在32位系统每个进程独享4GB空间的效果一样。这4GB空间的地址实际上是虚拟机地址,通过CR3寄存器映射到实际的物理地址上。而在开启了EPT机制的CPU上,GuestOS中同故宫CR3转换出来的GPA(Guest Physical Address)还要同故宫EPT机制转换到真是平台上的物理地址空间HPA(Host Physical Address)中。

EPT机制和IntelCPU上的分页机制类似。EPTP相当于多了一层CR3,即多了一层地址转换。

EPT页表可以包含最多4级也表结构。

- EPT PML4T(EPT Page Map Level-4 Table):表项是EPT PML4E。

- EPT PDPT(EPT Page Directory Pointer Table):表项时EPT PDPTE。

- EPT PDT(EPT Page Directory Table),表项是EPT PDE。

- EPT PT(EPT Page Table),表项是EPT PTE。

和分页机制一样,EPT支持3种页面。PDPTE的bit7置1,表示1GB大页面;PDE的bit7置1,表示2MB页面;如果bit7没有置位,那就是普通的4KB页面,GPA转换只需要经过两级EPT页表的转换流程;使用2MB页面时,GPA转换需要经过三级EPT页表转换流程;使用1GB页面时,GPA转换需要经过四级EPT页表转换流程。

在一开始不需要把所有的页面都配置好。在分页机制种,转换过程中遇到问题发生缺页异常#PF(Page Fault),通过捕获缺页异常将得到修正页面的机会。在EPT扩展页表机制下,如果从Guest OS的GPA转换到HPA的过程发生错误,将引发两类EPT故障,分别是EPT Violation和EPT Misconfiguration。当发生这两类故障的时候,处理器会产生#VMExit事件,通过在#VMExit中分析具体的原因将页面修正到正确的位置上。

0x02 VT技术的应用

该节运用VT技术实现了内存隐藏

2.1 编译运行ShadowWalt

2.2 分析Hypervisor

2.3 检测VT支持情况

2.4 VMCS的配置

2.5 EPT的配置

2.6 开启VT

2.7 内存隐藏的实现

0x03 VT调试方法

本章内容感觉会用到很多地方,笔者暂时用不到所以日后再进行补充。

文章评论